### Land Grid Array, LGA4189 Socket

#### 1. INTRODUCTION

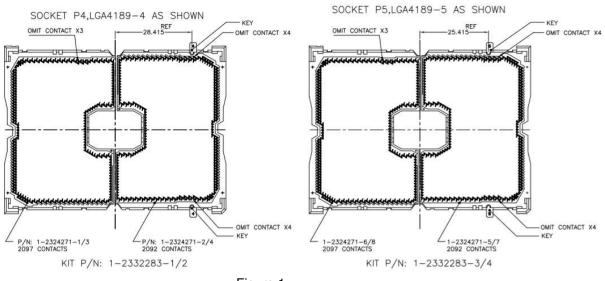

This specification covers the requirements for application of land grid array LGA4189 Socket onto printed circuit board (PC board). The socket contacts are arrayed about a cavity in the center of the socket with lead-free solder balls for surface mounting on the motherboard. The socket contacts have 0.8585×0.9906mm pitch (X by Y) with a hexagonal pattern and are arranged in two C-shape regions as illustrated in Figure 1. LGA4189 socket is used with combination of Bolster assembly, Back plate assembly and Carrier.

#### 1.1. Parts number and description

|                                   |                | Table 1. Part number and descr        | iption       |                      |  |  |  |  |

|-----------------------------------|----------------|---------------------------------------|--------------|----------------------|--|--|--|--|

| Socket P4/P5 Part Number          |                |                                       |              |                      |  |  |  |  |

| Kit P/N                           | Individual P/N | Final-Assemble                        | Plating Spec | Description          |  |  |  |  |

| 1-2332283-1                       | 1-2324271-1    | Right segment for LGA4189-4           | - 30u'       |                      |  |  |  |  |

|                                   | 1-2324271-2    | Left segment for LGA4189-4            |              |                      |  |  |  |  |

| 1-2332283-2                       | 1-2324271-3    | Right segment for LGA4189-4           | 45.2         | LGA4189-4, Socket P4 |  |  |  |  |

|                                   | 1-2324271-4    | Left segment for LGA4189-4            | - 15u'       |                      |  |  |  |  |

| 1-2332283-3                       | 1-2324271-5    | Right segment for LGA4189-5           | - 30u'       |                      |  |  |  |  |

|                                   | 1-2324271-6    | Left segment for LGA4189-5            | 30u          |                      |  |  |  |  |

| 1 000000 1                        | 1-2324271-7    | Right segment for LGA4189-5           | - 15u'       | LGA4189-5, Socket P5 |  |  |  |  |

| 1-2332283-4                       | 1-2324271-8    | Left segment for LGA4189-5            | 150          |                      |  |  |  |  |

| Socket P4/P5 Hardware Part Number |                |                                       |              |                      |  |  |  |  |

| TE Hardware P/N                   |                | Description                           |              |                      |  |  |  |  |

| 2-2330550-X (*)                   |                | TFLM Bolster Assy, Socket P4          |              |                      |  |  |  |  |

| 3-2330550-X (*)                   |                | TFLM Bolster Assy, Socket P5          |              |                      |  |  |  |  |

| 2-2330551-X (*)                   |                | ICX Backplate Assy, Socket P4/P5      |              |                      |  |  |  |  |

| 2-2330552-1                       |                | CPX-4 PHM Carrier Assy, Socket P4     |              |                      |  |  |  |  |

| 2-2330552-2                       |                | ICX Point PHM Carrier Assy, Socket P4 |              |                      |  |  |  |  |

| 3-2330552-1                       |                | CPX Point PHM Carrier Assy, Socket P5 |              |                      |  |  |  |  |

| 2-2330553-1                       |                | Dust Cover                            |              |                      |  |  |  |  |

Table 1 Part number and description

a: There are many package numbers, include kit package number and individual package number, detail please check customer drawing which show the relationship between package number and TE parts number.

For kit parts, include left and right segment, distinguish by key feature. b.

c. LGA4189 include 2 parts, they are LGA4189-4, LGA4189-5, the different point is the socket key location, please check customer drawing.

d. \* refer to customer drawing for detail

#### 1.2. Outline

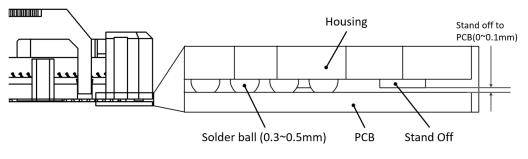

LGA4189 socket provides solder balls on bottom of socket to make contact to PC board. The housing holds an array of the contact. Please refer to figure 1.

Land Grid Array, LGA4189 Socket

#### 1.3. Notices

Figure 1

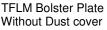

The sockets are placed on the PC board by automatic application tooling (typically vacuum pick and place). The PnP cap on the socket is used to facilitate this process, the socket must be with PnP cap attached before mounting on the PC board.

#### 1.4. Prohibitions

Do not touch contacts and solder balls

To prevent contact deformation and solder ball deformation, refrain to touch contacts and solder balls.

1.5 Basic terms and features of this product are provided as below (LGA4189 as shown).

Socket with PnP cap

Back Plate Assembly

CPX-4 PHM Carrier, P4

e TFLM Bolster Plate r With Dust Cover

ICX Point PHM Carrier, P4 CPX Point PHM Carrier, P5

MI TR

Figure2 Components

## Land Grid Array, LGA4189 Socket

### 2. REFERENCE MATERIAL

#### 2.1. Drawings

Customer Drawings for product part numbers are available from service network. If there is a conflict between the information contained in the Customer Drawings and the specification or with any other technical documentation supplied, the Customer Drawings shall take precedence. Customer drawing numbers: 2324271(individual package)/2332283(kit package).

2.2. Specification

Reference documents which pertain to this product are:

108-115149 : Product specification

501-115166 : Qualification test report

411-115008 : Instruction sheet

#### 3. **REQUIREMENTS**

#### 3.1. LGA package

The socket accepted 4189-position LGA package provided by Intel.

#### 3.2. Storage

A. Preferable condition

The sockets should remain in the shipping containers until ready for use to prevent deformation or oxidation to the solder balls. The sockets should be used on a first in, first out basis to avoid storage contamination that could adversely affect performance.

B. Chemical exposure

Prolonged exposure to ultraviolet light may deteriorate the chemical composition used in the socket material.

Do not store sockets near any chemical listed below as they may cause stress corrosion cracking in the solder balls.

Alkalies Ammonia Citrates Phosphates Citrates Sulfur Compounds Amines Carbonates Nitrites Sulfur Nitrites Tartrates

3.3. PC board

A. Material

The PC board material shall be glass epoxy (FR-4). B. Thickness

The PC board thickness shall be from 1.6mm to 3.2mm.

# 114-115024

04 Apr. 2023 Rev.E

## Land Grid Array, LGA4189 Socket

### C. Warpage

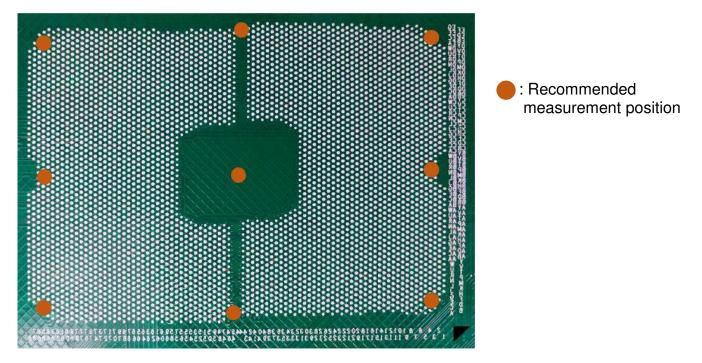

Maximum allowable bow of the PC board after reflow shall be 0.1mm per 25.4mm over the length of the socket grid area (Fig.4)

Figure4. Recommended measurement position of PC board warpage after SMT

#### D. Pads

The PC board circuit pads must be solder able in accordance with test specification EIA-364-52A.

E. Layouts and the volumetric zone for center cavity component

The circuit pads on the PC board must be precisely located to ensure proper placement and optimum performance of the socket. The PC board layout must be followed mechanical guide Intel provides.

#### 3.4. Solder paste characteristics

A. For sockets with lead free solder balls, alloy type shall be Sn / Ag / Cu

(This type of alloy has a melting point temperature of 217deg C)

B. Recommended flux incorporated in the paste should be "no clean" type. Other fluxes, such as rosin mildly active (RMA) type, are acceptable. DO NOT WASH THE SOCKET.

#### 3.5. Stencil design

Recommended stencil design is 0.127mm thickness with 0.48mm hole diameter.

#### 3.6 Oxygen concentration

Recommended O<sub>2</sub> concentration is around 1000~1500PPM.

### Land Grid Array, LGA4189 Socket

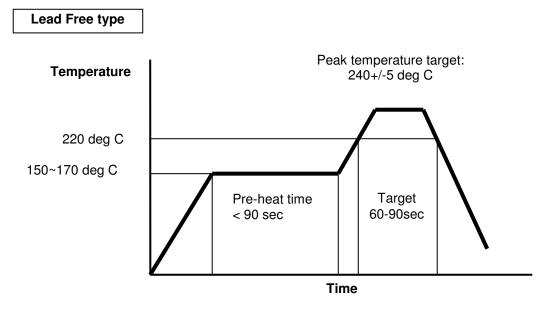

### 3.7. Soldering

The sockets should be soldered using hot air convection or nitrogen oven with a minimum of seven or eight chambers (zone) recommended. The solder paste should be applied using an automatic screening process.

Due to many variables involved with the reflow process (i.e. board size and thickness, component density, count and orientation), it is recommended that trial runs be conducted under actual manufacturing condition to ensure product and process compatibility. Reference reflow temperature profiles at solder ball positions are shown in the Fig.5.

Temperature at pick-up cap should be 260degC maximum.

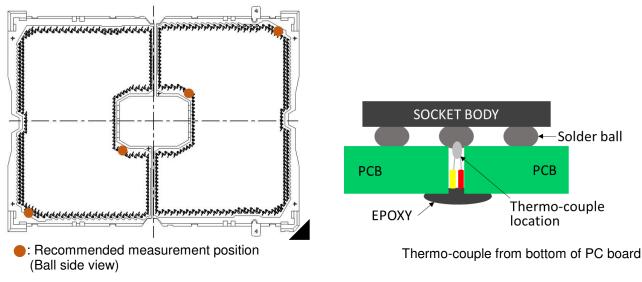

Temperature measurement points should be on the surface of the pads under the solder ball of the socket. (Fig.6) Temperature range in socket area should be less than 15deg C.

#### Figure6.Recommended temperature measurement position for SMT

### Land Grid Array, LGA4189 Socket

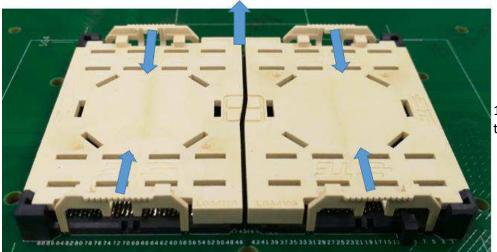

#### 3.8. Socket placement

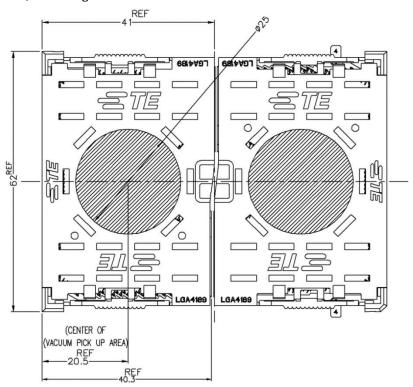

The socket is supplied with JEDEC tray. Refer to the customer drawing for the parts position in the tray. PnP cap assembled on the socket is for socket pick and place process. The center of gravity position refers to customer drawing. (Fig.7)

LGA4189 socket weights up to 15.18g each segment, balance between appropriate nozzle selection and head traverse rate. When placing the socket on the board, make sure that the solder balls are aligned with the matching pads before seating the socket onto the board.

Caution: The socket must be handled only by the outer perimeter of the socket to avoid deformation, contamination, or damage to the solder balls.

Figure7. Recommended pick up area

#### 3.9. Checking Installed Socket

The housing must be seated on the PC board with recommended dimension shown in Fig.8 .

Figure8. After SMT on PC board

The PnP cap on top of the socket must be removed right before CPU installation (the device must not be installed unless this pick-up cap is removed). Please refer to "arrow" on PnP cap to remove the PnP cap. *Note: Due to the tight pattern associated with these solder balls, inspection techniques must provide a clear picture of possible areas of shorting, X-ray or electrical test equipment will be used to inspect solder joints.*

# 114-115024

## Land Grid Array, LGA4189 Socket

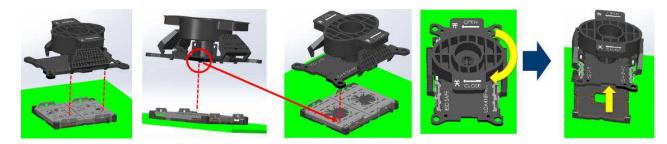

#### 3.10 Remove PnP cap operation

Customer can remove PnP cap by hand as Fig 9a shown. Grasp the tab of PnP cap with a force, tab deformation,

PnP cap separated from housing body, then pull vertically.

TE recommend remove PnP cap by PnP cap removal via tool as Fig 9b shown, which designed by Intel to avoid contact deformation. PnP cap removal via tool information and application, please refer to 411-115008.

2. Pick up vertical to remove PnP cap

1. Along the center to press the latch

Fig 9a Remove PnP cap

Fig 9b Remove PnP cap by tool

#### 3.11 Repair or rework

The socket is not repairable. Discard and replace any defective or damaged socket. Do not re-use the socket after removing it from the PC board.

The rework process specification is shown in Table 2 for LGA4189 socket (lead free), this is for customer reference, detail customer can follow its process.

Recommended rework profile measurement positions are at solder ball pad surface, same with Fig.6. Housing surface should be monitored also.

# Land Grid Array, LGA4189 Socket

| Table 2                                    |                                                |  |  |  |  |  |

|--------------------------------------------|------------------------------------------------|--|--|--|--|--|

| Socket LGA4189 Parameters                  | Specification                                  |  |  |  |  |  |

| Placement force                            | 0 grams (paste application)                    |  |  |  |  |  |

| Rework Ambient                             | Air (Nitrogen might result in contact wick)    |  |  |  |  |  |

| Solder Joint Peak Reflow Temperature (PRT) | 230 to 250°C                                   |  |  |  |  |  |

| Time Above ≥ 220°C                         | 60 to 120 seconds                              |  |  |  |  |  |

| Maximum Body Temperature                   | Never exceed component body temperature ≥260°C |  |  |  |  |  |

| Component Delta T (ΔT)                     | ≤15°C                                          |  |  |  |  |  |

| Soak Temp & Time                           | Paste dependent; consult paste manufacturer.   |  |  |  |  |  |

| Rising Ramp Rate below 150°C (+)           | 0.5 to 2.5°C/sec                               |  |  |  |  |  |

| Rising Ramp Rate between 205°C and 215°C   | 0.35 to 0.75°C/sec                             |  |  |  |  |  |

| (+)                                        |                                                |  |  |  |  |  |

| Falling Ramp Rate (-)                      | 0.50 to 2.0°C/sec                              |  |  |  |  |  |

#### 3.12 Heat sink load

Static compressive load from heat sink, Bolster assy and Back plate assy must meet the requirement shown in Table 3.

| Table 3                               |               |  |  |  |  |

|---------------------------------------|---------------|--|--|--|--|

| Maximum static total compressive load | 1557N(350lbf) |  |  |  |  |

| Minimum static total compressive load | 747N (168lbf) |  |  |  |  |

| REV | REV. RECORD PR      |           | ARED                    | CHECK   |                         | APPROVAL |                         |

|-----|---------------------|-----------|-------------------------|---------|-------------------------|----------|-------------------------|

| В   | Correct Typo        | Gabby Lin | 24 <sup>th</sup> Sep'20 | Bill Lv | 24 <sup>th</sup> Sep'20 | Simon Li | 24 <sup>th</sup> Sep'20 |

| С   | Correct Typo        | Gabby Lin | 22 <sup>th</sup> Oct'20 | Bill Lv | 22 <sup>th</sup> Oct'20 | Simon Li | 22 <sup>th</sup> Oct'20 |

| D   | Correct Typo        | Gabby Lin | 28 <sup>th</sup> Jan'21 | Bill Lv | 28 <sup>th</sup> Jan'21 | Simon Li | 28 <sup>th</sup> Jan'21 |

| Е   | Stencil spec update | Boney T V | 04 <sup>th</sup> Apr'23 | Bill Lv | 04 <sup>th</sup> Apr'23 | Kim Jin  | 04 <sup>th</sup> Apr'23 |